Asian Journal of Chemistry; Vol. 25, Supplementary Issue (2013), S409-S410

# ASIAN JOURNAL OF CHEMISTRY

www.asianjournalofchemistry.co.in

## On Simulation of Single Electron Transistor†

A. Jain\*, A. Ghosh and S.K. Sarkar

Department of Electronics and Telecommunication Engineering, Jadavpur University, Kolkata-700 032, India

\*Corresponding author: Fax: +91 33 24572404; Tel: +91 33 24572404; E-mail: amit2\_8@yahoo.co.in

AJC-12889

To explore the single electronics technology efficiently we need a proper simulation environment. In this paper we have investigated three basic simulation methodologies of single electron transistor *i.e.*, Monte carlo, Master equation and spice macro modeling. Basically the analytical modeling of single electron transistors is based on orthodox theory of single electron tunneling. Here we have compared the simulation results of V-I characteristics of single electron transistor obtained from analytical modeling, macro modeling and Monte carlo method.

Key Words: Single electron transistor, Macro model, SIMON, MIB model, Monte carlo method, Coulomb oscillation.

#### INTRODUCTION

Single electron transistor is being chosen as the most promising candidate for future VLSI solutions due to its nano feature size, ultra low power dissipation, CMOS compatible fabrication process<sup>1</sup>. The operation of the single electronics circuits are based on the controlled manipulation of individual electrons through a potential barrier. The most important matter regarding single electronics circuits is the reliability, which depends on circuit structure, parameter values, temperature and random background charges. In our previous work we have analyzed the reliability and the effect of temperature on the stability of single electronics circuits<sup>2</sup>.

There are three different approaches to the simulation of single electronics circuits: SPICE macro-modeling, Monte carlo based and master equation based. The Monte carlo method takes long time to simulate single electronics circuit with larger no of islands as it follows the stochastic integration approach to compute the tunnel times for all possible events. In master equation method one needs to solve a set of equations deterministically to get the simulation results<sup>3</sup>. All the relevant states a circuit can occupy should be known before writing the equations, which is the main problem of master equation method. For small single electronics circuits master equation method is faster than the Monte carlo approach, but for circuits with larger no of nodes master equation method becomes infeasible. In macro modeling approach an equivalent circuit representing the single electron transistor is designed using basic micro electronics components such as diodes, voltage sources, current sources and resistors. As in the macro modeling

approach the equivalent circuit representing the device has no physical accordance with the device itself so it is less accurate compare to other two simulation methodologies. But as this approach does not depend on calculating the probability of tunnel events it is much faster compare to monte carlo based simulation and master equation based method.

## SINGLE ELECTRON TRANSISTOR

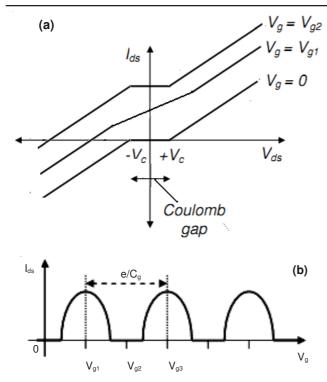

The main two phenomena of single electron transistor operation are coulomb blockade or coulomb gap and coulomb oscillations. The ideal drain current *versus* drain to source voltage characteristics for symmetric tunnel junction is shown in Fig. 1(a). As can be observed from Fig. 1(a) the coulomb gap is bounded by critical voltage (V<sub>c</sub>), which is needed across the tunnel junction for a tunnel event to occur. The value of the critical voltage is given by<sup>4</sup>.

$$V_{\rm C} = \frac{\rm e}{2(C_{\rm e} + C_{\rm i})}$$

The coulomb oscillation characteristics of a single electron transistor is shown in Fig. 1(b). It can be observed that with the increase in gate to source voltage the drain current oscillates periodically with period  $e/C_g$ . For each oscillation exactly one electron is transferred to the respective island<sup>5</sup>.

#### SIMULATION METHODS

The largely accepted simulation tool SIMON<sup>6</sup>, is based on the Monte carlo method<sup>7</sup>. In this method initially all the possible tunnel events along with their tunnel rates are considered and finally random tunnel times are calculated for all

S410 Jain et al. Asian J. Chem.

Fig. 1. (a) Ideal I<sub>ds</sub> vs. V<sub>ds</sub> characteristics of a single electron transistor for symmetric tunnel junctions. Here Vc is the charging voltage of the single electron transistor. (b) Coulomb oscillation characteristics of a single electron transistor for a fixed value of drain to source voltage

events. Then the event with smallest tunnel time will happen first and charges and voltages will be updated correspondingly. New tunnel rates are again calculated and a new winner is again chosen through stochastic sampling.

The analytical modeling approach of single electron transistor is based on master equation method<sup>7</sup>. The first analytical model of single electron transistor has been proposed by Uchida *et al.*<sup>9</sup>, which is only applicable to the symmetric SET. Though the model does not account for background charge effect it is well suited for high temperature applications<sup>1</sup>. Then Mahapatra *et al.*<sup>1</sup> proposed a model which is mostly known as MIB model, which can be applied for single or multiple-gate, symmetric or asymmetric devices. The MIB model can also explain the background charge effect very well.

The next approach which does not depend on the physics of the device and fastest of all the simulation methods is the macro modeling approach. As it does not consider the device physics it is less accurate compare to the other methods. Yu *et al.*<sup>8</sup> first proposed a macro model of a single electron transistor which works efficiently for single electronics circuits. The main drawback of Yu's model is the drain current is not equal to zero for zero gate to source voltage in the coulomb blockade region. Later, Wu and Lin<sup>10</sup> solved this problem by incorporating two back to back diode in the model to make the gate to source current negligibly small.

#### SIMULATION RESULTS

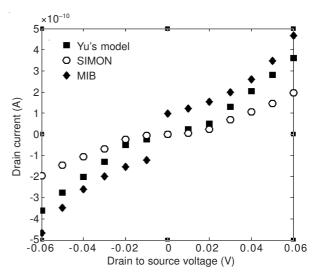

The simulation results obtained from SIMON simulator, Spice macro modeling and MIB model is shown in Fig. 2. We have dumped all the simulation results in a single plot so that all the simulation methods can be compared with each other and also with ideal one. It can be observed that among all the methods the results obtained from SIMON closely follows the ideal one. So for circuits with less no of nodes SIMON is the best option in terms of accuracy. But the major problem with SIMON simulator is that we can not co-simulate SET and MOSFET here which can be done in Spice environment either using MIB model or by macro modeling.

Fig. 2. Comparison of the  $I_{ds}$ - $V_{ds}$  characteristics for zero gate to source voltage obtained from Yu's model, SIMON and verilog-A model MIB under the condition of  $R_D = R_S = 100 \text{ M}\Omega$ ,  $C_{TD} = C_{TS} = 1.6 \text{ aF}$  and T = 30 K

#### Conclusion

In this work, we have studied different methods for simulation of single electron transistor based circuits. Here we have comapred different methods considering there speed and accuracy. The V-I characteristics of single electron transistor simulated using MIB model, Monte carlo method and SIMON simulator has been shown and compared with the ideal characteristics. The advantage and disadvantage for zero gate to source voltage obtained from Yu's model, SIMON and verilog-A model MIB of different methods are discussed briefly so that one can go for a particular simulation method according to the requirements.

## **ACKNOWLEDGEMENTS**

One of the authors (SKS) acknowledged the financial support from CSIR.

### REFERENCES

- S. Mahapatra, A.M. Ionescue and K. Banerjee, *IEEE Electron Device Lett.*, 23, 366 (2002).

- N.B. Singh, S. Deb, A.K. De and S.K. Sarkar, J. Elec. Dev., 9, 342 (2011).

- 3. A.M. Ferrenberg, D.P. Landau and Y.J. Wong, Phys. Rev. Lett., 69 (1992).

- S. Mahapatra, Hybrid CMOS Single Electron Transistor Device and Circuit Design, Artech House Publication (2006).

- Y. Takahashi, A. Fujiwara, Y. Ono and K. Murase, Proceedings of the 30<sup>th</sup> IEEE International Symposium on Multiple-Valued Logic, pp. 411-420 (2000).

- C. Wasshuber, H. Kosina and S. Selberherr, *IEEE Trans. On Computer Aided Design of Integrated Circuits and Systems*, 16, 9 (1997).

- 7. C. Wasshuber, Computational Single Electronics, Springer Verlag (2001).

- 8. Y.S. Yu, S.W. Hwang and D. Ahn, *IEEE Trans. Elec. Devices*, **46**, 8 (1999).

- 9. K. Uchida, K. Matsuzawa, J. Koga, R. Ohba, S. Takagi and A. Toriumi, *Jpn. J. Appl. Phys.*, **39**, 2321 (2000).

- 10. Y.L. Wu and S.T. Lin, Nanotechnology, 3, 321 (2003).